Design of a full adder circuit

Table Of Contents

Chapter ONE

1.1 Introduction1.2 Background of Study

1.3 Problem Statement

1.4 Objective of Study

1.5 Limitation of Study

1.6 Scope of Study

1.7 Significance of Study

1.8 Structure of the Research

1.9 Definition of Terms

Chapter TWO

2.1 Overview of Full Adder Circuits2.2 Historical Development of Full Adder Circuits

2.3 Types of Full Adder Circuits

2.4 Basic Principles of Full Adder Circuits

2.5 Applications of Full Adder Circuits

2.6 Advantages and Disadvantages of Full Adder Circuits

2.7 Innovations in Full Adder Circuit Design

2.8 Comparison of Full Adder Circuits with Other Logic Gates

2.9 Challenges in Designing Full Adder Circuits

2.10 Future Trends in Full Adder Circuit Technology

Chapter THREE

3.1 Research Methodology Overview3.2 Research Design and Approach

3.3 Data Collection Methods

3.4 Sampling Techniques

3.5 Data Analysis Procedures

3.6 Research Instruments

3.7 Ethical Considerations

3.8 Validity and Reliability of Research

Chapter FOUR

4.1 Data Analysis and Interpretation4.2 Findings from the Study

4.3 Comparison of Results with Hypotheses

4.4 Discussion of Key Findings

4.5 Implications of Findings

4.6 Recommendations for Future Research

4.7 Practical Applications of Research

4.8 Limitations of the Study

Chapter FIVE

5.1 Summary of Research Findings5.2 Conclusion and Interpretation

5.3 Contributions to the Field

5.4 Practical Implications

5.5 Recommendations for Action

5.6 Areas for Future Research

5.7 Conclusion Remarks

5.8 Final Thoughts and Acknowledgments

Project Abstract

AbstractThe design of a full adder circuit is a fundamental aspect of digital electronics and plays a crucial role in arithmetic operations within digital systems. A full adder is a combinational circuit that performs the addition of three input bits and generates a sum bit and a carry out bit. This research project focuses on the detailed design and implementation of a full adder circuit using basic logic gates. The primary objective of this project is to develop an efficient full adder circuit that can accurately perform binary addition while minimizing the propagation delay and power consumption. The design process involves understanding the underlying principles of binary addition, Boolean algebra, and logic gate operations. By utilizing this knowledge, a systematic approach is taken to create a full adder circuit that meets the desired specifications. The design methodology includes the use of logic gates such as AND, OR, and XOR gates to implement the logic functions required for addition. The circuit is structured in a way that allows for the proper handling of input bits and the generation of the correct sum and carry out bits. Special attention is given to optimizing the layout of the circuit to ensure efficient signal propagation and reduce the overall complexity. Simulation tools such as SPICE are employed to validate the functionality of the full adder circuit and to analyze its performance under various input conditions. The simulation results are used to verify the correctness of the design and to identify any potential issues that may arise during practical implementation. Furthermore, considerations are made for scaling the full adder circuit to higher bit-width designs by cascading multiple full adders together. This scalability aspect is essential for building more complex arithmetic circuits that require the addition of larger binary numbers. Overall, the successful design of a full adder circuit involves a comprehensive understanding of digital logic principles, careful circuit implementation, and thorough testing and validation. By following a systematic design approach and utilizing simulation tools, a reliable and efficient full adder circuit can be developed for use in various digital systems and applications.

Project Overview

INTRODUCTION

According to the novel by Mehdi Ghasemi, Mohammad Hussein Moaiyeri, Keivan Navi, published on Jan 10, 2012. Due to high power consumption and difficulties with minimizing the CMOS transistor size, molecular electronics has been introduced as an emerging technology. Further, there have been noticeable advances in fabrication of molecular wires and switches and also molecular diodes can be used for designing different logic circuits.

Considering their technology novel, they use molecules as the active components of the circuit, for transporting electric charge. They presented a full adder circuit based on molecular electronics. This full adder is consisted of resonant tunneling diodes and transistors which are implemented via molecular electronics. The area occupied by this kind of full adder would be much times smaller than the conventional designs and it can be used as the building block of more complex molecular arithmetic circuits.

Ramya Menon C. and Vinod Pangracious 16 Jan 2012 published a novel which declares that; in a multiprocessor system on chip (MPSOC) IC the processor is one of the highest heat dissipating devices. The temperature generated in an IC may vary with floor plan of the chip. The novel proposes an integration and thermal analysis methodology to extract the peak temperature and temperature distribution of 2-dimensional and 3-dimensional multiprocessor system-on-chip. As we know the peak temperature of chip increases in 3-dimensional structures compared to 2-dimensional ones due to the reduced space in intra-layer and inter-layer components.

In sub-nanometer scale technologies, it is inevitable to analyze the heat developed in individual chip to extract the temperature distribution of the entire chip. With the technology scaling in new generation ICs more and more components are integrated to a smaller area. Along with the other parameters threshold voltage is also scaled down which results in exponential increase in leakage current. This has resulted in rise in hotspot temperature value due to increase in leakage power. They analyzed the temperature developed in an IC with four identical processors at 2.4 GHz in different floor plans. The analysis has been done for both 2D and 3D arrangements. In the 3D arrangement, a three layered structure has been considered with two Silicon layers and a thermal interface material (TIM) in between them. Based on experimental results they propose a methodology to reduce the peak temperature developed in 2D and 3D integrated circuits.

HISTORY

Until the late 1970’s, most minicomputer did not have a multiple instruction, and so programmers used a “multiply routine” which repeatedly shifts and accumulates partial results, often written using loop unwinding. Mainframe computers had multiply instructions. The Motorola 6809, introduced in 1978, was one of the earliest microprocessors with a dedicated hardware multiplying instruction. It did the same sorts of shifts and adds as a “multiply routine”, but implemented in the microcode of the MUL instruction [citation needed].

As more transistors per chip became available due to Larger Scale Integration (LSI), it become possible to put enough adders on a single chip to sum all the partial products at once, rather than reuse a single adder to handle each partial product one at a time. Because common digital signal processing algorithms spend most of their time on multiplying, digital signal processor designers sacrifice a lot of chip area in order to make the multiply-accumulate unit often used up most of the chip area of early DSPs.

RESEARCH METHODOLOGY

SIMILAR WORKS BASED ON FULL ADDER CIRCUITS

Some designs of adder cells can be found in the figures 1 to 6. These six different adder cells are simulated in 0.18 µm CMOS technology and tested separately. All these cells are optimum in power dissipation and Power delay product (PDP). The conventional adder shown in figure 1 is implemented with 28 Transistors in CMOS technology. Conventional adder circuits do not function well below one volt supply. Figure 2 shows the Complementary Pass-transistor Logic (CPL) adder. Among the pass transistor logic styles, CPL has the best performance and the lowest power delay product.

The Transmission Function full Adder (TFA), which is shown in figure 3, uses 16 transistors. Pull-up and pull-down logic is used to drive the load the same as the complementary pass logic. Figure 4 shows the Transmission Gate full adder (TG). TG adder includes 20 transistors, and generates a+b and its complement to produce the sum and carry signals. It uses complementary input signals (a, b, c) as the complementary CMOS full adder. This full adder uses only 14 transistors to make the adder function. The circuit occupies less area in comparison with other CMOS full adder cells. At end, another full adder with 26 transistors is presented in figure 6.

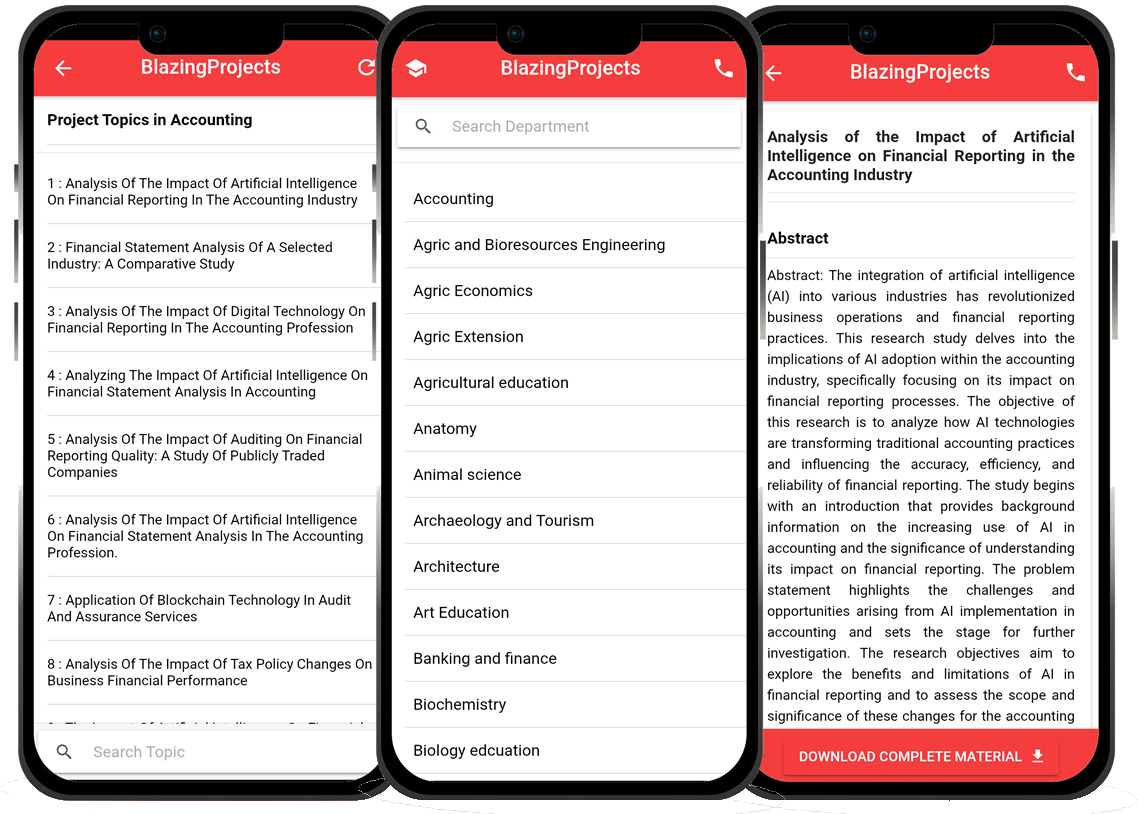

Blazingprojects Mobile App

📚 Over 50,000 Project Materials

📱 100% Offline: No internet needed

📝 Over 98 Departments

🔍 Software coding and Machine construction

🎓 Postgraduate/Undergraduate Research works

📥 Instant Whatsapp/Email Delivery

Related Research

Design and Implementation of an Intelligent Energy Management System for Smart Build...

The project titled "Design and Implementation of an Intelligent Energy Management System for Smart Buildings" focuses on the development of a sophisti...

Design and Implementation of an Intelligent Energy Management System for Smart Grid ...

The project topic "Design and Implementation of an Intelligent Energy Management System for Smart Grid Applications" focuses on the development and de...

Design and Implementation of Smart Home Energy Management System using IoT Technolog...

The project on "Design and Implementation of Smart Home Energy Management System using IoT Technology" aims to develop a cutting-edge system that leve...

Design and Implementation of a Smart Energy Management System for Residential Buildi...

The project topic "Design and Implementation of a Smart Energy Management System for Residential Buildings" focuses on the development and application...

Design and implementation of an IoT-based smart energy management system for residen...

The project "Design and Implementation of an IoT-Based Smart Energy Management System for Residential Buildings" aims to address the growing need for ...

Design and implementation of a smart grid system for optimizing energy distribution ...

The project on "Design and implementation of a smart grid system for optimizing energy distribution and management" aims to address the pressing need ...

Design and Implementation of an Energy-Efficient Smart Home System using Internet of...

The project, "Design and Implementation of an Energy-Efficient Smart Home System using Internet of Things (IoT) Technology," aims to revolutionize res...

Design and Implementation of a Smart Grid System for Efficient Energy Management...

The project topic, "Design and Implementation of a Smart Grid System for Efficient Energy Management," focuses on developing a smart grid system to en...

Design and implementation of a smart energy management system for residential buildi...

The project on "Design and Implementation of a Smart Energy Management System for Residential Buildings using Internet of Things (IoT) Technology" aim...