Design and construction of an electronic dice display with audio unit

Table Of Contents

<p> </p><p>FIG 1.0 and gate diagram<br>Fig 1.1 capacitor diagram<br>Fig 1.2 seven segment diagram<br>Fig 3.01 block schematic diagram of an electronic dice display<br>Fig 3.02 block schematic diagram of an audio unit<br>Fig 3.03 555 timer schematic circuit diagram<br>Fig 3.04 555 timer block diagram<br>Fig 3.05 555 timer configuration<br>Fig 3.06 pin-out connection of a 555 timer<br>Fig 3.07a 555 timers in astable mode<br>Fig 3.07b timing diagram<br>Fig 3.08 Jk flip flop symbol<br>Fig 3.09 delay flip-flop from Jk flip-flop<br>Fig 3.10a delay flip-flop from JK flip-flop<br>Fig 3.10b D flip-flop timing diagram<br>Fig 3.11 D type flip-flop in TTL<br>Fig 3.12 Quad-and gate symbol<br>Fig 3.13a Circuit block diagram of a digital counter<br>Fig 3.13b Output wave forms<br>Fig 3.14a circuit block diagram of mod 10 counter<br>Fig 3.14b output wave forms<br>Fig 3.15 Mod 6 counter using decade counter<br>Fig 3.16 functional logic diagram of BCD to decimal decoder<br>Fig 3.17 seven segment display layout arrangement<br>Fig 3.18 seven segment display connections<br>Fig 3.19 BCD to seven segment block diagram<br>Fig 3.20 7447 BCD to seven segment decoder driver functional<br>Fig 4.01 top view of 7414<br>Fig 4.02 counter configuration for the 7490A<br>Fig 4.03 top view of 7474<br>Fig 4.04 top view of SN 7447<br>Fig 4.05 top view of common unode display<br>Fig 5.01 output wave of 555 timers Table 3.1 time table for sK flip-flop<br>Table 3.2 delay flip-flop forms flip-flop<br>Table 3.4 and logic gate truth table<br>Table 3.5 table of counter output in various forms.<br>Table 3.7 bid to seven segment decoder truth table<br>Table 4.1a BCD count sequence<br>Table 5.0 procedure chart<br>Table 5.1 system flowchart<br>Table 6.0 program design<br>Table 6.1 program flowchart<br> <br>Title page ii<br>Approval page iii<br>Dedication iv<br>Acknowledgement v<br>Abstract vi<br>Organization of work viii<br>List of figures x<br>List of table xii<br>Table of content xiii</p><p><b>

Chapter ONE

<br>INTRODUCTION </b> 1<br>1.0 Statement of problem 1<br>1.1 purpose of study 2<br>1.2 Aims and objectives 2<br>1.3 Scope 3<br>1.4 Limitations 3<br>1.5 Definitions of terms 5</p><p><b>Chapter TWO

</b><br>Literature Review 9</p><p><b>Chapter THREE

</b><br>Description and Analysis of the Existing System 15<br>Organization structure 16<br>Objectives of the existing system 17</p><p><b>Chapter FOUR

</b><br>Design of the New System 18<br>Output specification and design 20<br>Input specification and design 29<br>File design 38<br>Procedure chart 39<br>System flow chart 41<br>System requirement 42</p><p><b>Chapter FIVE

</b><br>Implementation 47<br>Program flowchart 49</p><p><b>CHAPTER SIX</b><br>Documentation 51</p><p><b>CHAPTER SEVEN<br>Recommendation and Conclusion 53 </b><br>7.1 Recommendation 53<br>7.2 Conclusion 53<br><b>Reference 55</b></p> <br><p></p>Project Abstract

This work deals extensively with the design and construction of an electronic dice display (EOD) with audio unit. The device displays the of a ludo dice in numerical form and also produces sound as it displays the number.

The device works with principle of chance employee by ludo game players. The output of the display is usually very rapid that the player does actually sex the number when the device is switched on so that it will purely be a game of chance. When the off key is pressed, a patellar number is displayed and this number is the number, the player got.

The operation of the device starts by the generation of a pulse frequency. The pulse frequency (square wave signal) generated by times (555 times) by connecting in an instable multibibrator. The output from this timer is used in clocking the binary counter (mod to counter) but this counter is biased to count just from zero through six (0-6) as we have in a lodo game dice. To achieve this bias in the mod 10 counter, the output from Qo, Q1 and Q2 were connected to the reset pins so that once the counter finishes the count of six or goes back to zero.

The result from the binary counter is then fed to the decoder driver before connecting it to seven segment so that the decoder will be able to covert the binary values to the decimal values that are being used in the ludo game dice. The seven segment then displays the numbers by lighting the diodes that make up that particular value.

This device is being regulated by a latch (4-edge triggered flip-flop) which has two switches, one is used for putting the power supply and the other two push switches for the working of the dice display.

Project Overview

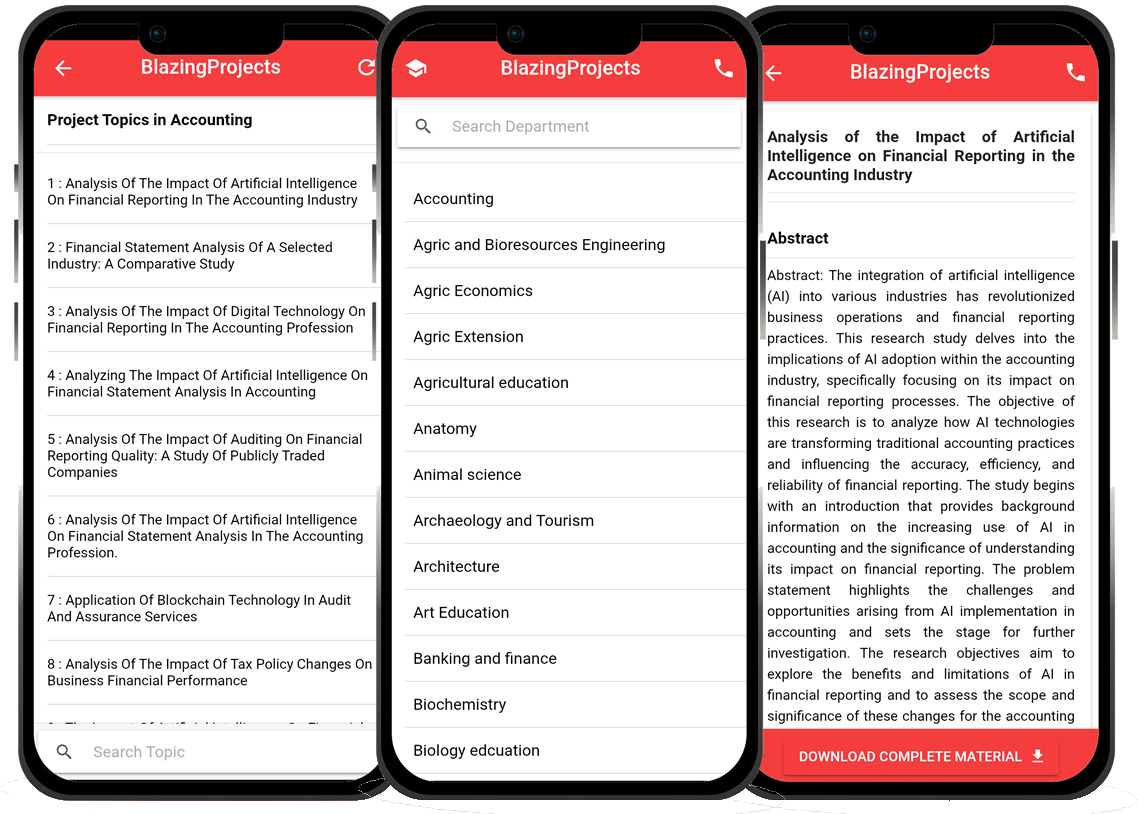

Blazingprojects Mobile App

📚 Over 50,000 Project Materials

📱 100% Offline: No internet needed

📝 Over 98 Departments

🔍 Software coding and Machine construction

🎓 Postgraduate/Undergraduate Research works

📥 Instant Whatsapp/Email Delivery

Related Research

Predicting Disease Outbreaks Using Machine Learning and Data Analysis...

The project topic, "Predicting Disease Outbreaks Using Machine Learning and Data Analysis," focuses on utilizing advanced computational techniques to ...

Implementation of a Real-Time Facial Recognition System using Deep Learning Techniqu...

The project on "Implementation of a Real-Time Facial Recognition System using Deep Learning Techniques" aims to develop a sophisticated system that ca...

Applying Machine Learning for Network Intrusion Detection...

The project topic "Applying Machine Learning for Network Intrusion Detection" focuses on utilizing machine learning algorithms to enhance the detectio...

Analyzing and Improving Machine Learning Model Performance Using Explainable AI Tech...

The project topic "Analyzing and Improving Machine Learning Model Performance Using Explainable AI Techniques" focuses on enhancing the effectiveness ...

Applying Machine Learning Algorithms for Predicting Stock Market Trends...

The project topic "Applying Machine Learning Algorithms for Predicting Stock Market Trends" revolves around the application of cutting-edge machine le...

Application of Machine Learning for Predictive Maintenance in Industrial IoT Systems...

The project topic, "Application of Machine Learning for Predictive Maintenance in Industrial IoT Systems," focuses on the integration of machine learn...

Anomaly Detection in Internet of Things (IoT) Networks using Machine Learning Algori...

Anomaly detection in Internet of Things (IoT) networks using machine learning algorithms is a critical research area that aims to enhance the security and effic...

Anomaly Detection in Network Traffic Using Machine Learning Algorithms...

Anomaly detection in network traffic using machine learning algorithms is a crucial aspect of cybersecurity that aims to identify unusual patterns or behaviors ...

Predictive maintenance using machine learning algorithms...

Predictive maintenance is a proactive maintenance strategy that aims to predict equipment failures before they occur, thereby reducing downtime and maintenance ...